IO系统解决的主要问题是对各种形式的信息进行输入和输出的控制

| I/O 软件 | I/O 硬件 |

|---|---|

| 包括:驱动程序、用户程序、管理程序。 | 包括:外部设备、设备控制器和接口、I/O 总线。 |

|

实现方式: I/O 指令:由 CPU 执行。 通道指令:由 通道(一个专门处理I/O的处理器)执行。 |

1. IO设备

定义:计算机与外部世界交换信息的硬件设备。

| 输入设备 | 如键盘、鼠标。 | |

|---|---|---|

| 输出设备 |

打印机 |

按工作方式分类:点阵打印机 / 针式打印机,喷墨式打印机,激光打印机 按能否打出汉字分类(此分类较传统):点阵打印机(可以打印汉字),活字打印机(如传统英文打字机,不能灵活打印汉字) |

|

显示器 |

按器件原理分类: CRT(阴极射线管)显示器 LCD(液晶)显示器 LED(发光二极管)显示器 工作方式:点阵方式。屏幕图像由无数个独立的像素点组成。 主要性能参数: 屏幕大小:以屏幕对角线长度表示(如英寸)。 分辨率:屏幕能表示的像素个数。表示方法:宽 × 高(如 1920 × 1080)。分辨率越高,图像越细腻。 灰度级:像素点的亮暗差别(在彩色显示器中即颜色数)。灰度级/颜色数越多,图像越逼真。 刷新频率:单位时间内(通常为秒)扫描整个屏幕内容的次数。频率过低会导致屏幕闪烁。 显示存储器(VRAM):又名刷新存储器。为了持续刷新屏幕,必须将一整幅屏幕图像(一帧)的信息存储在这里。 容量计算: 带宽计算: |

|

| 输入/输出设备 | 如磁盘存储器、光盘存储器(既可存入数据,也可读出数据)。 | |

2. IO接口

2.1. 概念

别名:I/O 控制器、设备控制器。

角色:主机(CPU、内存)与外部设备之间的“桥梁”或“交接界面”。

存在原因:外设不能直接连接到系统总线上,必须通过 I/O 接口。

2.2. 功能

| 地址译码 | 识别 CPU 发送的 I/O 地址,选中对应的接口寄存器(选中对应的外设)。 |

|---|---|

| 数据交换与控制 |

实现主机与 I/O 设备之间的数据传送。 传递 CPU 的控制命令。 检测并向 CPU 报告设备的状态(如忙、就绪、错误)。 |

| 缓冲与驱动 |

缓冲:解决主机与外设之间的速度差异(数据缓存)。 驱动:提供足够的电信号驱动能力。 |

| 数据转换 | 进行数据格式和类型的转换(如串行⇄并行、电压电平转换) |

| 支持 I/O 方式 | 支持程序查询、中断、DMA 等多种数据交换方式。 |

| 控制与定时 | 提供操作时序,协调数据传送。 |

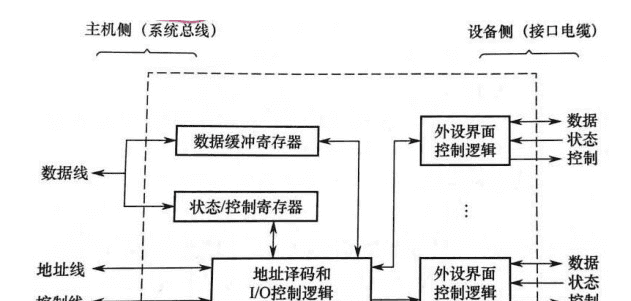

2.3. 组成与连接

接口内部核心部件:一组可被 CPU 访问的寄存器。

连接方式:

主机侧:通过系统总线与 CPU 和内存相连。

外设侧:与外部设备相连。

总线信号作用:

数据线:传送数据、控制命令、状态信息。

地址线:指定要访问的接口内部寄存器的地址。

控制线:传送读/写、仲裁、握手等控制信号。

2.4. 分类

| 串行接口 | 逐位传输。速度低、距离长。 |

|---|---|

| 并行接口 | 多位同时传输。速度高、距离短。 |

| 程序查询接口 | CPU 主动轮询设备状态。 |

|---|---|

| 中断接口 | 设备就绪后主动通知 CPU。 |

| DMA 接口 | 由 DMA 控制器直接在内存与外设间传输数据,无需 CPU 介入。 |

| 通道控制接口 | 功能更强的专用处理机,可执行通道程序管理 I/O。 |

| 同步接口 | 数据传输由统一的时钟信号控制。 |

|---|---|

| 异步接口 | 采用“请求-应答”握手方式,适应不同速度的设备。 |

| 可编程接口 | 通过编程改变接口功能 |

|---|---|

| 不可编程接口 |

2.5. I/O 端口

I/O 端口:I/O 接口电路中那些可被 CPU 直接访问的寄存器(如数据寄存器、状态寄存器、控制寄存器)。

IO端口想要被CPU访问,就必须要对各个端口进行编址,每个端口对应一个端口地址。

I/O 端口地址:每个端口都有一个唯一的编号(地址),CPU 通过这个地址来访问它。

两种主要的编址方式:

| 特性 | 统一编址(存储器映射式) | 独立编址(I/O 映射式) |

|---|---|---|

| 地址空间 | I/O 端口与内存单元共享同一个地址空间。 | I/O 端口拥有独立的、与内存分开的地址空间。 |

| 访问指令 | 使用普通的访存指令(如 |

需要使用专用的 I/O 指令(如 |

| 控制信号 | CPU 只需提供一组“存储器读/写”控制信号。 | CPU 需提供“存储器读/写”和“I/O 读/写”两组控制信号。 |

| 优点 | 1. 指令集简单、灵活。 2. 访问端口像访问内存一样方便。 3. I/O 地址空间可以很大。 |

1. 程序清晰,I/O 操作与内存操作在指令上区分开。 2. 不占用内存地址空间。 |

| 缺点 | 1. 占用部分内存地址空间。 2. 地址译码可能更复杂(整个内存地址空间都需要参与译码)。 |

1. 指令集需要专门设计 I/O 指令,灵活性较差。 |

| 典型架构 | MIPS, ARM, PowerPC, RISC-V | x86 架构 |

3. IO方式

I/O 控制方式主要有四种,根据数据传输速率和控制复杂度划分:

1️⃣低速设备:程序查询方式、程序中断方式。2️⃣高速设备:DMA 方式、通道方式。

从程序查询到通道,I/O 控制方式的发展历程是不断将 CPU 从繁重的 I/O 事务中解放出来,提高整个系统效率的过程。

其核心趋势是:CPU 干预越来越少,硬件控制越来越强,并行度越来越高。

3.1. 程序查询方式

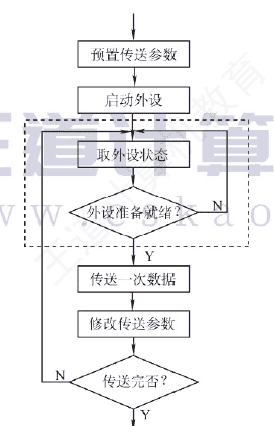

| 核心思想 | I/O 操作完全由 CPU 执行程序控制,CPU 主动、轮询检查设备状态。 | |

|---|---|---|

| 工作流程 |

1️⃣预置参数:CPU 执行初始化程序,设置传送地址、计数器等。 2️⃣启动设备:向 I/O 接口发出命令字,启动 I/O 设备。 3️⃣读取状态:从外设接口读取设备状态。 4️⃣查询等待:CPU 不断循环查询设备状态,直到设备就绪。➜ “踏步”现象 独占查询:一旦设备被启动,CPU就一直持续查询接口状态,CPU花费100%的时间用于I/O操作,此时外设和CPU完全串行工作。 定时查询:CPU周期性地查询接口状态,每次总是等到条件满足才进行一个数据的传送,传送完成后返回到用户程序。定时查询的时间间隔与设备的数据传输速率有关。 5️⃣数据传送:设备就绪后,进行一次数据传送。 6️⃣修改参数:更新内存地址,计数器减1。 7️⃣判断结束:检查传送是否完成。若未结束,跳回步骤(3)继续查询。 |

|

| 特点 |

缺点:CPU 与 I/O 设备串行工作,CPU 效率极低(大量时间用于等待)。 优点:硬件结构简单,易于实现。 |

|

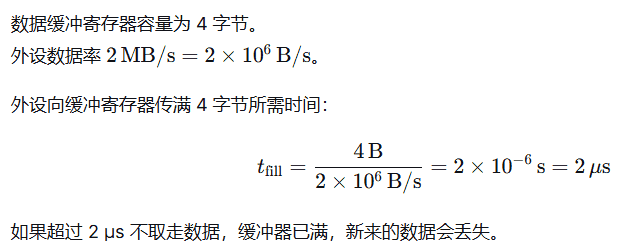

🌼例题

已知条件:

主频

➡️CPU 时钟周期

(每条指令需要 4 个时钟周期)外设数据率

I/O 接口数据缓冲寄存器 32 位 = 4 字节采用定时查询方式每次 I/O 操作(即每次查询并传输数据)CPU 执行 10 条指令

问题1:外设最多间隔多长时间查询一次才不丢失数据?

问题2:CPU 用于外设 I/O 的时间占 CPU 总时间的百分比至少是多少?

1️⃣每次查询的 CPU 时间开销:

每次查询执行 10 条指令,CPI = 4,主频 500 MHz。

每条指令时间:

10 条指令时间:

2️⃣每秒查询次数

最大间隔

3️⃣每秒总 I/O 时间

4️⃣占 CPU 总时间百分比

3.2. 程序中断方式⭐

| 核心思想 | I/O 设备完成后主动向 CPU 发出请求,CPU 中断当前程序,转去处理 I/O 事务,完成后返回。实现了 CPU 与 I/O 设备的并行工作。 | |

|---|---|---|

| 中断请求 |

中断源:引起中断的事件或设备。 中断请求标记:一个寄存器,每位对应一个中断源,1 表示有中断请求。 中断类型: 可屏蔽中断 (INTR):可以被 CPU 忽略(通过“关中断”指令)。优先级较低。 不可屏蔽中断 (NMI):必须立即响应,如电源掉电、硬件故障。优先级最高。 |

|

|---|---|---|

|

中断响应判优 ⭐ 具体应用见多重中断例题 |

响应优先级:硬件电路(排队器)决定的、CPU 响应中断请求的顺序。固定不变。 一般优先级规则: |

|

| 处理优先级:通过中断屏蔽字技术,可以动态调整的中断服务程序的执行顺序。 | ||

| CPU 响应中断的条件 |

中断源有请求。 CPU 处于开中断状态(对于可屏蔽中断而言)。 当前指令执行完毕(在指令周期的末尾响应)。 |

|

| 中断识别 |

1️⃣向量中断 中断向量:中断源的 唯一的类型号对应的 中断服务程序的 入口地址。 中断向量表:存放所有中断向量的内存区域。 过程:CPU 根据中断类型号,计算出中断向量在表中的位置(地址),然后取出该地址中的内容(中断向量)并送入 PC,从而开始执行服务程序。 2️⃣非向量中断:软件查询法(第5章已介绍)。 |

|

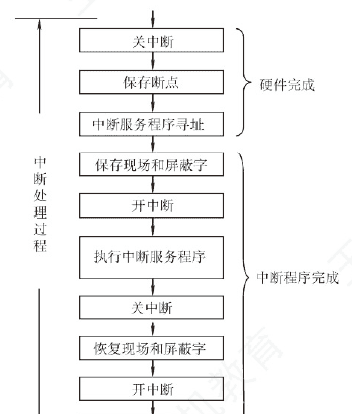

| 中断处理过程 |

关中断:保护现场不被新的中断打断。 保存断点:将程序计数器(PC)和程序状态字(PSW)压栈。 中断服务程序寻址:获取中断服务程序的入口地址。 保存现场和屏蔽字:保护通用寄存器等现场信息。 开中断:允许更高级的中断请求,实现中断嵌套。 执行中断服务程序:处理 I/O 数据传送或其他事务。 关中断:保证恢复现场时不被干扰。 恢复现场和屏蔽字:恢复之前保存的寄存器和状态。 开中断:为返回后响应新中断做准备。 中断返回:通过中断返回指令,恢复断点(PC和PSW),回到原程序。 |

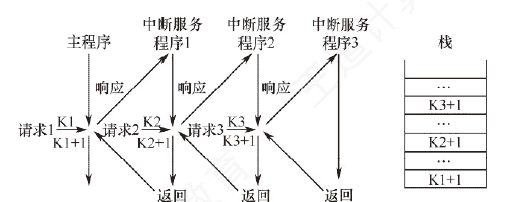

中断隐指令:步骤 1-3 是由硬件直接完成的操作,不是一条具体的指令,故称为“隐指令”。 |

|

单重中断 |

在执行中断服务程序期间,关闭中断,不响应任何新的中断请求。 |

|---|---|

| 多重中断 |

在执行低级中断服务程序时,允许响应更高级的中断请求。 实现条件: ①在中断服务程序中提前设置开中断指令。 ②优先级别高的中断源有权中断优先级别低的中断源。 |

|

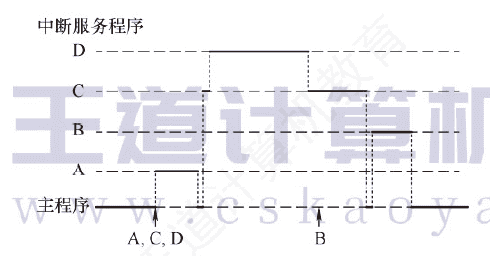

中断处理优先级是指多重中断的实际优先级处理次序,可以利用中断屏蔽技术动态调整,从而可以灵活地调整中断服务程序的优先级,使中断处理更加灵活。 若不使用中断屏蔽技术,则处理优先级和响应优先级相同。 |

|

|

现代计算机中,每个中断源都有一个屏蔽触发器,1表示屏蔽该中断源的请求,0表示可以正常申请,所有屏蔽触发器组合在一起构成屏蔽字寄存器,其内容称为屏蔽字。

1)中断屏蔽字 中断屏蔽字格式:按顺序 A B C D,1 表示屏蔽,0 表示开放。 A:优先级最高,屏蔽所有(包括自己),屏蔽字 = 1111 D:仅被 A 中断,屏蔽 B、C、D,不屏蔽 A,屏蔽字 = 0111 C:被 A、D 中断,屏蔽 B、C,不屏蔽 A、D,屏蔽字 = 0110 B:被 A、D、C 中断,只屏蔽 B,屏蔽字 = 0100

2)CPU 执行程序轨迹 用户程序 [屏蔽字 0110,B 请求被屏蔽,继续执行完] 处理优先级起作用

|

3.3. DMA 方式⭐

| 核心思想 | 在外设与内存之间开辟一条直接数据通路,数据传送不经过 CPU,由 DMA 控制器 这个硬件来管理。CPU 仅在开始和结束时参与。 |

|---|---|

| 特点 |

①数据传输不需要 CPU 干预,CPU 与外设并行工作效率高。 ②主存可被 CPU 和 DMA 控制器交替访问。 ③传送前需要 CPU 预处理,传送后需要 中断后处理。 |

| DMA 控制器的功能 |

①接收外设的 DMA 请求。 ②向 CPU 申请总线使用权。 ③管理数据传送:发出内存地址、读写控制信号、计数等。 ④传送结束后,向 CPU 发出中断请求进行后处理。 |

| DMA 传送方式(CPU 与 DMA 访问内存的冲突解决) |

停止 CPU 访问:DMA 传送时,CPU 完全停止访问内存。控制简单,但 CPU 利用率低。 DMA 与 CPU 交替访存:将 CPU 周期分为两部分,一部分专供 DMA 使用。不需要申请总线,效率高,但要求 CPU 周期 > 内存存取周期。 周期挪用(周期窃取) ✅ 常用:DMA 趁 CPU 不访问内存时“挪用”总线周期。若冲突,则 DMA 优先,因为 I/O 数据不及时处理可能会丢失。DMA 每次传送一个数据(字/字节)后即释放总线。 |

| DMA 传送过程 |

预处理 (CPU负责):CPU 初始化 DMAC,设置内存起始地址、传送字节数、传送方向等。然后 CPU 继续执行原程序。 数据传送 (DMAC负责): 外设准备好后,向 DMAC 发请求。 DMAC 向 CPU 申请总线。 CPU 完成当前总线周期后,释放总线控制权给 DMAC。 DMAC 控制外设与内存直接进行数据传送。 后处理 (CPU负责): 数据块传送完毕后,DMAC 向 CPU 发中断请求。 CPU 执行中断服务程序,检查 DMA 操作是否正确,决定是否继续传送等。 |

| 特性 | 中断方式 | DMA 方式 |

|---|---|---|

| 数据交换 | 通过CPU程序中转 | 在内存和外设间直接进行,不经过CPU |

| 响应时间 | 只能在指令执行结束时 | 可在每个机器周期结束时 |

| CPU干预 | 传送过程需要CPU频繁干预 | 仅在预处理和后处理时需要CPU干预 |

| 请求优先级 | 较低 | 较高(防止数据丢失) |

| 处理能力 | 能处理异常事件 | 仅用于数据传输 |

| 靠程序传送 | 靠硬件传送 |

3.4. 通道方式

| 核心思想 | 通道是一个专用处理器,拥有自己的指令系统(通道指令),能执行通道程序来管理 I/O 操作。可以看作是 DMA 方式的增强和发展,进一步减少了 CPU 的干预。 |

|---|---|

| 特点 |

是功能更强的 I/O 控制器,有专门的通道处理器。 通过执行存放在主存中的通道程序来管理 I/O,几乎不需要 CPU 干预。 通道程序的生成和管理由操作系统负责。 CPU 只需发出“启动I/O通道”指令即可。 |

| 通道的分类 |

选择通道: 连接多台高速设备(如磁盘),但一次只为一台设备服务。 通道数据传输率 = 所连接设备中速率最高的一台。 |

|

字节多路通道: 连接多台低速设备(如打印机、终端),以字节为单位,为多台设备交叉服务。 通道数据传输率 = 各设备传输率之和。 |

|

|

数组多路通道: 结合了以上两者的优点。连接多台高速设备,以数据块为单位,为多台设备交叉服务。 通道数据传输率 = 各设备传输率之和。 |

暂无评论内容