我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。

老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:

做到欲望极简,了解自己的真实欲望,不受外在潮流的影响,不盲从,不跟风。把自己的精力全部用在自己。一是去掉多余,凡事找规律,基础是诚信;二是系统思考、大胆设计、小心求证;三是“一张纸制度”,也就是无论多么复杂的工作内容,要在一张纸上描述清楚;四是要坚决反对虎头蛇尾,反对繁文缛节,反对老好人主义。

一直很喜欢发小老李QQ签名那句话—生活如逆水行舟,不进则退。农村做题家出来的汉子,我可能已经不具备享受快乐的权力,只有做个躬行的卒子,一步一个脚印往前走。

中年男人尽量避免陷入历史虚无主义,自己无需问“人活着为了什么?”,做自己该做之事,七八月只管播种,到了十一二月收获季节,自有收获。

先说结论:面向高阶自动驾驶,异构多核硬件架构成为趋势。

一、车载计算平台

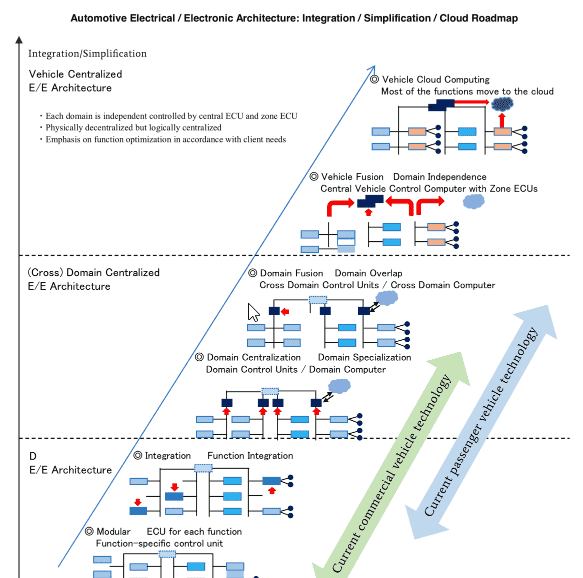

在高级别自动驾驶技术演进过程中,车载计算平台作为“智能汽车大脑”,其硬件架构设计直接决定了自动驾驶系统的感知精度、决策效率与控制安全性。当前,面向复杂路况与多任务处理需求,异构多核芯片硬件架构已成为车载计算平台的主流选择,通过整合不同类型计算单元的技术优势,实现“各司其职、协同高效”的运算效能。

自动驾驶域控制器作为计算平台的核心载体,需同时具备多传感器融合、高精度定位、实时路径规划、智能决策控制、车联网无线通讯及车内高速通讯等复合能力。实际应用中,域控制器通常需外接8-16路摄像头、4-6颗毫米波雷达、1-2颗激光雷达以及惯性测量单元(IMU)等设备,承担图像识别、点云处理、环境建模等海量数据运算任务。尤其面向L3及以上高阶自动驾驶,单一类型芯片因架构特性限制,难以同时满足多接口兼容、高算力输出、低延迟响应等多重需求,因此采用异构芯片硬件方案成为必然选择,其具备芯片选型灵活、功能模块可配置拓展、算力按需堆砌等核心优势,为自动驾驶系统的迭代升级提供硬件基础。

典型的车载计算平台异构分布硬件架构,主要由CPU计算单元、AI单元和控制单元三大部分组成,各单元分工明确且通过高速互联总线实现数据协同。

-> CPU计算单元:系统控制与核心算法中枢

CPU计算单元通常由车规级多核CPU集群构成,目前主流采用ARM架构,凭借单核高主频、强逻辑处理能力的特性,成为整个计算平台的“指挥中枢”。其硬件设计重点在于通过复杂的缓存层级(L1/L2/L3 Cache)和任务调度机制,保障高精度浮点数串行计算的稳定性与实时性。在自动驾驶系统中,CPU不仅负责软硬件资源的全局管理与任务优先级分配,还承担着路径规划、决策控制等核心算法的执行工作——例如基于高精地图与实时路况信息生成最优行驶路径,结合环境感知结果做出超车、避让、减速等驾驶决策,同时协调其他计算单元的工作状态,确保系统整体运算流程的有序性。

-> AI单元:海量数据处理与算力输出核心

AI单元是异构硬件平台中算力的最主要来源,专门应对自动驾驶场景下大规模浮点数并行计算需求,其性能直接决定了多传感器数据处理的效率与精度。目前主流的AI加速芯片选型包括GPU、FPGA、ASIC三类:GPU擅长高并行度的图像与点云数据处理,适用于深度学习模型推理;FPGA具备可编程性,可根据算法需求灵活调整硬件逻辑,适合快速迭代的研发阶段;ASIC则为特定算法定制硬件架构,能效比与算力密度最优,多用于量产车型。在系统运行中,内核系统负责对AI加速引擎及相关芯片资源进行动态分配与调度,AI单元则通过多传感器数据融合技术,对摄像头图像、激光雷达点云、毫米波雷达信号等进行同步处理,提取道路目标、交通标识、车道线等关键信息,为CPU的规划决策模块提供精准输入。

-> 控制单元:车辆执行与功能安全保障

控制单元聚焦于车辆动力学控制与功能安全保障,虽不要求极高的算力输出,但对可靠性与安全性有着严苛要求。其硬件基础源于传统车辆控制器MCU(微控制单元),通过冗余设计与故障检测机制,实现车辆横纵向控制功能——例如控制电子助力转向系统调整行驶方向,调节电机或发动机输出扭矩控制车速,同时满足汽车功能安全最高等级ASIL-D的要求。在异构架构中,控制单元作为“执行终端”,接收CPU下发的决策指令并转化为具体的车辆控制信号,同时实时监控自身及其他计算单元的工作状态,一旦检测到异常便触发安全冗余机制,确保车辆行驶过程中的绝对安全。

二、高阶自动驾驶域控制器的必备特点

高性能的车载计算平台是高阶自动驾驶的必备,除了异构多核的硬件架构外,分布弹性可扩展、丰富的 I/O 接口资源、高内存带宽、车规与功能安全等也是核心域控制器特点。

-> 硬件异构—多芯片协同的算力基础

面向高阶自动驾驶的计算平台需兼容多类型、多数量传感器,单一芯片难以满足复杂的接口需求与算力承载。因此,需采用“CPU+XPU”的异构硬件方案(前文已详细阐述),通过CPU负责系统控制与任务调度,XPU(如GPU、FPGA、ASIC等)专注于感知计算、决策规划等并行任务,实现算力资源的高效分配与协同。

-> 分布弹性可扩展—适配不同自动驾驶等级的动态需求

车载计算平台需具备弹性扩展能力,以匹配不同等级自动驾驶的功能需求。针对L3及以上高阶自动驾驶场景,随着自动驾驶等级的提升,车载智能计算基础平台对算力、接口数量的需求将持续增长。除提升单芯片算力密度外,硬件单元可通过复制堆叠实现横向扩展,同时自动驾驶操作系统需具备弹性适配能力,可平滑兼容新增硬件单元,最终达成系统整体算力提升、接口扩展与功能完善的目标。

-> 丰富的I/O接口资源—多传感器数据接入的关键支撑

高阶自动驾驶感知系统依赖海量传感器数据,涵盖车载摄像头、激光雷达、毫米波雷达、超声波雷达、组合导航、IMU、V2X模块等,因此丰富的I/O接口资源是自动驾驶域控制器的核心竞争力之一。各传感器接口类型具有明确适配性:车载摄像头多采用GMSL或FPDLink数据接口;激光雷达普遍使用Ethernet接口(目前以普通Ethernet为主);毫米波雷达通过CAN FD总线传输数据;超声波雷达采用LIN总线;组合导航与惯导常用RS232串口;V2X模块则依托Ethernet接口实现数据交互。此外,平台还需集成PCIe、USB、I2C、SPI等常见高速与低速接口,满足系统扩展需求。

-> 高内存带宽—突破数据处理瓶颈的性能保障

自动驾驶芯片平台需实时接入并处理大量传感器数据流,导致内存面临巨大压力,系统往往呈现“Memory-Bound”(内存受限)特性。在此背景下,内存带宽直接决定了系统数据吞吐能力的理论上限,是保障感知、决策等核心任务低延迟执行的关键指标,需通过高性能内存控制器与存储架构设计实现带宽优化。

-> 车规与功能安全—车载场景的硬性合规要求

与消费级产品不同,车规级计算平台对安全性与可靠性有着严苛标准,需满足AEC-Q100(车规级芯片认证)、ISO 26262(功能安全标准)等行业规范。其中,ISO 26262将功能安全等级划分为ASIL-A至ASIL-D,自动驾驶域控制器根据功能安全需求,通常需达到ASIL-B或ASIL-D级别,通过硬件冗余、故障检测与容错机制等设计,确保系统在复杂车载环境下的稳定运行。

搁笔分享完毕!

愿你我相信时间的力量

做一个长期主义者

© 版权声明

文章版权归作者所有,未经允许请勿转载。如内容涉嫌侵权,请在本页底部进入<联系我们>进行举报投诉!

THE END

暂无评论内容